# Lógica Digital (1001351)

ufere

Circuitos Sequenciais: Latches e Flip-flops

Prof. Ricardo Menotti menotti@ufscar.br

Atualizado em: 1 de abril de 2024

Departamento de Computação Centro de Ciências Exatas e de Tecnologia Universidade Federal de São Carlos Prof. Luciano de Oliveira Neris Ineris@ufscar.br

Circuitos Sequenciais

### Objetivos

Nesta aula vamos aprender sobre:

- Circuitos lógicos que podem armazenar informações;

- Latches e Flip-flops, os quais armazenam um único bit.

#### Necessidade

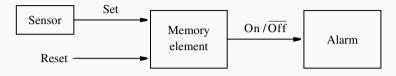

Figure 5.1 Control of an alarm system.

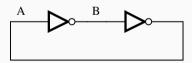

**Figure 5.2** A simple memory element.

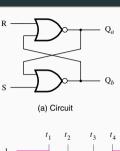

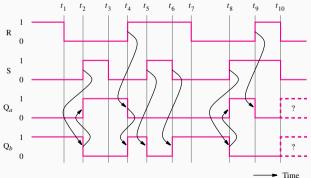

#### Latch básico

| S | R | $Q_a$ | $Q_b$ | _           |

|---|---|-------|-------|-------------|

| 0 | 0 | 0/1   | 1/0   | (no change) |

| 0 | 1 | 0     | 1     |             |

| 1 | 0 | 1     | 0     |             |

| 1 | 1 | 0     | 0     |             |

|   |   |       |       |             |

(b) Characteristic table

## Latch com habilita (gated latch)

5

## Latch com habilita (gated latch)

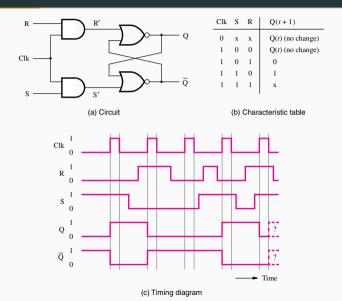

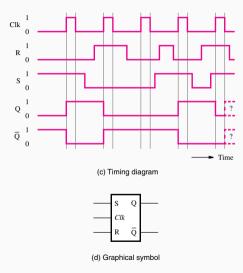

Figure 5.5 Gated SR latch.

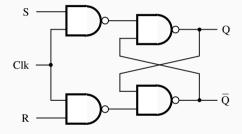

#### Latch construído com portas NAND

Figure 5.6 Gated SR latch with NAND gates.

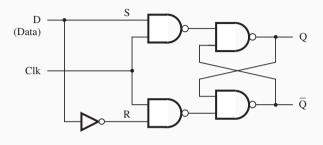

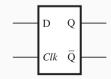

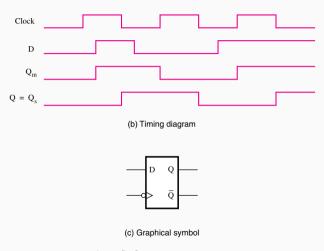

#### Latch D

(a) Circuit

| Clk | D | Q(t+1) |

|-----|---|--------|

| 0   | x | Q(t)   |

| 1   | 0 | 0      |

| 1   | 1 | 1      |

(c) Graphical symbol

#### Latch D

**Figure 5.7** Gated D latch.

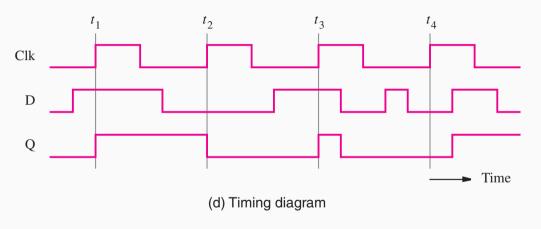

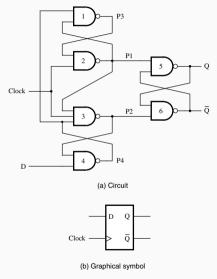

## Flip-flop D Mestre/Escravo

### Flip-flop D Mestre/Escravo

Figure 5.9 Master-slave D flip-flop.

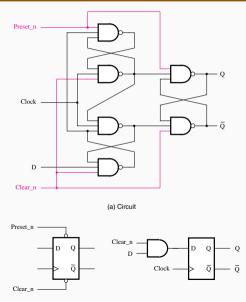

# Flip-flop D com borda positiva (subida)

Figure 5.11 A positive-edge-triggered D flip-flop.

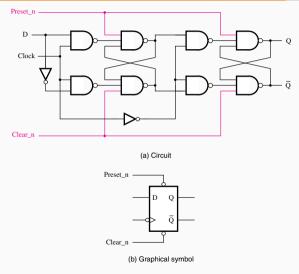

## Flip-flop D Mestre/Escravo com Clear e Preset

Figure 5.12 Master-slave D flip-flop with Clear and Preset.

# Flip-flop D Mestre/Escravo com borda positiva

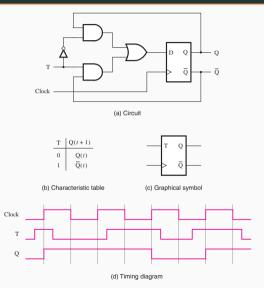

## Flip-flop T

Figure 5.15 T flip-flop.

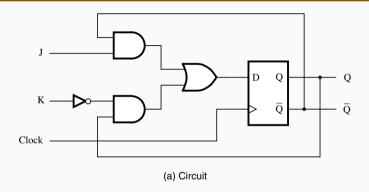

## Flip-flop JK

$$\begin{array}{c|cccc} J & K & Q(t+1) \\ \hline 0 & 0 & Q(t) \\ 0 & 1 & 0 \\ 1 & 0 & 1 \\ 1 & 1 & \overline{Q}(t) \\ \hline \end{array}$$

## Bibliografia

- Brown, S. & Vranesic, Z. Fundamentals of Digital Logic with Verilog Design, 3rd Ed., Mc Graw Hill, 2009

- https://www.falstad.com/circuit/e-nandff.html

# Lógica Digital (1001351)

uferen

Circuitos Sequenciais: Latches e Flip-flops

Prof. Ricardo Menotti menotti@ufscar.br

Atualizado em: 1 de abril de 2024

Departamento de Computação Centro de Ciências Exatas e de Tecnologia Universidade Federal de São Carlos Prof. Luciano de Oliveira Neris Ineris@ufscar.br