Conjunto de instruções (ARM)

Prof. Ricardo Menotti (menotti@ufscar.br)

Atualizado em: 26 de abril de 2021

## Departamento de Computação

Centro de Ciências Exatas e de Tecnologia Universidade Federal de São Carlos

## Sobre a arquitetura ARM

- Desenvolvida na década de 80 pela Advanced RISC Machines Ltd.

- Mais de 10 bilhões de processadores vendidos todos os anos (2016);

- ARM não vende processadores diretamente, mas licencia para outros fabricantes;

## **Particularidade**

- A maioria dos conjuntos de instruções só permite que saltos sejam executados condicionalmente;

- Os processadores ARM possuem um mecanismo de execução condicional de instruções:

- Todas as instruções contém um campo de condição, indicando as circunstâncias de execução;

- Reusando o hardware de comparação, aumenta-se efetivamente o número de instruções;

- Isso elimina a necessidade de muitos saltos;

- Os processadores ARM possuem uma unidade de deslocamento (*Barrel Shifter*) para o segundo operando da ULA:

- Se o fator for um imediato, a operação não adiciona nenhum ciclo à instrução;

- Isso pode ser usado, por exemplo, para escalar endereços;

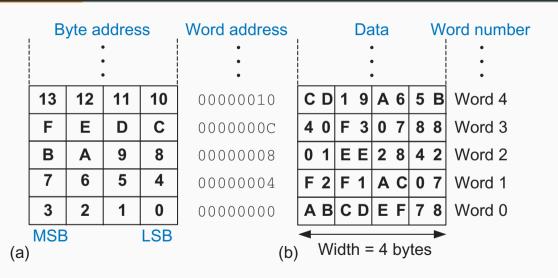

## Endereçamento

# Registadores [Harris and Harris(2016)]

**Table 6.1** ARM register set

| Name     | Use                                          |  |  |

|----------|----------------------------------------------|--|--|

| R0       | Argument / return value / temporary variable |  |  |

| R1–R3    | Argument / temporary variables               |  |  |

| R4–R11   | Saved variables                              |  |  |

| R12      | Temporary variable                           |  |  |

| R13 (SP) | Stack Pointer                                |  |  |

| R14 (LR) | Link Register                                |  |  |

| R15 (PC) | Program Counter                              |  |  |

# Sintaxe [Harris and Harris(2016)]

## **Code Example 6.8 READING MEMORY**

## **High-Level Code**

## **ARM Assembly Code**

a = mem[2];

```

; R7 = a MOV R5, \#0 ; base address = 0 LDR R7, [R5, \#8] ; R7 <= data at memory address (R5+8)

```

## **Code Example 6.9 WRITING MEMORY**

## **High-Level Code**

## **ARM Assembly Code**

mem[5] = 42;

MOV R1, #0 ; base address = 0

MOV R9, #42

STR R9, [R1, #0x14]; value stored at memory address (R1+20) = 42

# Operações Lógicas [Harris and Harris(2016)]

# Source registers

| R1 | 0100 0110 | 1010 0001 | 1111 0001 | 1011 0111 |

|----|-----------|-----------|-----------|-----------|

| R2 | 1111 1111 | 1111 1111 | 0000 0000 | 0000 0000 |

# Assembly code

## Result

| AND | R3, | R1, | R2 | R3 | 0100 0110 | 1010 0001 | 0000 0000 | 0000 0000 |

|-----|-----|-----|----|----|-----------|-----------|-----------|-----------|

| ORR | R4, | R1, | R2 | R4 | 1111 1111 | 1111 1111 | 1111 0001 | 1011 0111 |

| EOR | R5, | R1, | R2 | R5 | 1011 1001 | 0101 1110 | 1111 0001 | 1011 0111 |

| BIC | R6, | R1, | R2 | R6 | 0000 0000 | 0000 0000 | 1111 0001 | 1011 0111 |

| MVN | R7, | R2  |    | R7 | 0000 0000 | 0000 0000 | 1111 1111 | 1111 1111 |

# Deslocamentos [Harris and Harris(2016)]

|         |       |               | Source register |           |           |           |  |

|---------|-------|---------------|-----------------|-----------|-----------|-----------|--|

|         |       | R5            | 1111 1111       | 0001 1100 | 0001 0000 | 1110 0111 |  |

| Assemb  | ly Co | de            |                 | Re        | sult      |           |  |

| LSL R0, | R5,   | #7 <b>R0</b>  | 1000 1110       | 0000 1000 | 0111 0011 | 1000 0000 |  |

| LSR R1, | R5,   | #17 <b>R1</b> | 0000 0000       | 0000 0000 | 0111 1111 | 1000 1110 |  |

| ASR R2, | R5,   | #3 <b>R2</b>  | 1111 1111       | 1110 0011 | 1000 0010 | 0001 1100 |  |

| ROR R3, | R5,   | #21 <b>R3</b> | 1110 0000       | 1000 0111 | 0011 1111 | 1111 1000 |  |

Source register

# Deslocamentos [Harris and Harris(2016)]

#### Source register

R5 1111 1111 0001 1100 0001 0000 1110 0111

#### **Assembly Code**

#### Result

| LSL | R0, | R5, | #7 F  | 80 | 1000 1110 | 0000 1000 | 0111 0011 | 1000 0000 |

|-----|-----|-----|-------|----|-----------|-----------|-----------|-----------|

|     |     |     |       |    |           |           |           | 1000 1110 |

|     |     |     |       |    |           |           |           | 0001 1100 |

| ROR | R3, | R5, | #21 F | 23 | 1110 0000 | 1000 0111 | 0011 1111 | 1111 1000 |

#### Source registers

|    |           |           | 0001 0110 |           |

|----|-----------|-----------|-----------|-----------|

| R6 | 0000 0000 | 0000 0000 | 0000 0000 | 0001 0100 |

#### Assembly code

LSL R4, R8, R6 R

ROR R5, R8, R6 R

#### Result

|            |           |           | 0000 0000 |           |

|------------|-----------|-----------|-----------|-----------|

| <b>R</b> 5 | 1100 0001 | 0110 1110 | 0111 0000 | 1000 0001 |

# CPU Flags [Harris and Harris(2016)]

**Table 6.2 Condition flags**

| Flag | Name     | Description                                                     |

|------|----------|-----------------------------------------------------------------|

| N    | Negative | Instruction result is negative, i.e., bit 31 of the result is 1 |

| Z    | Zero     | Instruction result is zero                                      |

| С    | Carry    | Instruction causes a carry out                                  |

| V    | oVerflow | Instruction causes an overflow                                  |

# Execução condicional [Harris and Harris(2016)]

| cond | Mnemonic     | Name                                | CondEx                                |

|------|--------------|-------------------------------------|---------------------------------------|

| 0000 | EQ           | Equal                               | Z                                     |

| 0001 | NE           | Not equal                           | $\overline{Z}$                        |

| 0010 | CS/HS        | Carry set / unsigned higher or same | C                                     |

| 0011 | CC/LO        | Carry clear / unsigned lower        | $\overline{C}$                        |

| 0100 | MI           | Minus / negative                    | N                                     |

| 0101 | PL           | Plus / positive or zero             | $\overline{N}$                        |

| 0110 | VS           | Overflow / overflow set             | V                                     |

| 0111 | VC           | No overflow / overflow clear        | $\overline{V}$                        |

| 1000 | HI           | Unsigned higher                     | $\overline{Z}C$                       |

| 1001 | LS           | Unsigned lower or same              | $Z$ OR $\overline{C}$                 |

| 1010 | GE           | Signed greater than or equal        | $\overline{N \oplus V}$               |

| 1011 | LT           | Signed less than                    | $N \oplus V$                          |

| 1100 | GT           | Signed greater than                 | $\overline{Z}(\overline{N \oplus V})$ |

| 1101 | LE           | Signed less than or equal           | $Z$ OR $(N \oplus V)$                 |

| 1110 | AL (or none) | Always / unconditional              | Ignored                               |

# Unsigned Signed A = $1001_2$ A = 9 A = -7B = $0010_2$ B = 2 B = 2 A - B: 1001 NZCV = $0011_2$ (a) $\frac{+ 1110}{10111}$ HS: TRUE GE: FALSE

|       |    |     | Uns | signed  | Signed |

|-------|----|-----|-----|---------|--------|

| A = 0 | 10 | 12  | A = | 5       | A = 5  |

| B = 1 | 10 | 12  | B = | 13      | B = -3 |

| A – E | 3: | 010 | 1   | NZCV =  | 10012  |

|       | +  | 001 | 1_  | HS: FAL | .SE    |

| (b)   |    | 100 | 0   | GE: TRI | JE     |

Figure 6.7 Signed vs. unsigned comparison: HS vs. GE

# Execução condicional [Harris and Harris(2016)]

```

\label{eq:R2} \begin{split} &R2 = 0 \times 80000000, \ R3 = 0 \times 00000001 \\ &R2 - R3 = 0 \times 80000000 + 0 \times FFFFFFF = 0 \times 7FFFFFFF \Rightarrow C=1, \ V=1, \ N=0, \ Z=0 \end{split}

```

## **Code Example 6.10** CONDITIONAL EXECUTION

## **ARM Assembly Code**

```

CMP R2, R3

ADDEQ R4, R5, #78

ANDHS R7, R8, R9

ORRMI R10, R11, R12

EORLT R12, R7, R10

```

ADDEQ X ANDHS ✓ ORRMI X EORLT ✓

# Salto [in]condicional [Harris and Harris(2016)]

#### **Code Example 6.11** UNCONDITIONAL BRANCHING

#### **ARM Assembly Code**

#### **Code Example 6.12 CONDITIONAL BRANCHING**

```

MOV RO, #4 ; R0 = 4

ADD R1, RO, RO ; R1 = RO + RO = 8

CMP RO, R1 ; set flags based on RO-R1 = -4. NZCV = 1000

BEO THERE ; branch not taken (Z!=1)

ORR R1, R1, #1 ; R1 = R1 OR 1 = 9

THERE

ADD R1, R1, #78 ; R1 = R1 + 78 = 87

```

# Estrutura If/Else [Harris and Harris(2016)]

#### **Code Example 6.14** IF/ELSE STATEMENT

#### **High-Level Code**

```

if (apples == oranges)

f = i + 1;

else

f = f - i;

```

```

\begin{array}{lll} \mbox{ ; R0 = apples, R1 = oranges, R2 = f, R3 = i} \\ \mbox{ CMP R0, R1 } & \mbox{ ; apples == oranges?} \\ \mbox{ BNE L1 } & \mbox{ ; if not equal, skip if block} \\ \mbox{ ADD R2, R3, $\#1$} & \mbox{ ; if block: } f = i + 1 \\ \mbox{ B L2 } & \mbox{ ; skip else block} \\ \mbox{ L1 } & \mbox{ SUB R2, R2, R3 } & \mbox{ ; else block: } f = f - i \\ \mbox{ L2 } \\ \mbox{ } \end{array}

```

# Estrutura If/Else [Harris and Harris(2016)]

#### **Code Example 6.14** IF/ELSE STATEMENT

#### **High-Level Code**

```

if (apples == oranges)

f = i + 1;

else

f = f - i;

```

```

CMP RO, R1 ; apples == oranges?

ADDEQ R2, R3, \#1 ; f = i + 1 on equality (i.e., Z = 1)

SUBNE R2, R2, R3 ; f = f - i on not equal (i.e., Z = 0)

```

## Estrutura Case [Harris and Harris(2016)]

#### **Code Example 6.15** SWITCH/CASE STATEMENT

## **High-Level Code**

```

switch (button) {

case 1: amt = 20: break:

case 2: amt = 50: break:

case 3: amt = 100: break:

default: amt = 0:

//equivalent function using

//if/else statements

if (button == 1) amt = 20:

else if (button == 2) amt = 50:

else if (button == 3) amt = 100:

else

amt = 0:

```

```

: R0 = button . R1 = amt

CMP RO. #1

: is button 1?

MOVEQ R1, #20

: amt = 20 if button is 1

BEO DONE

: break

CMP RO. #2

· is button 2?

MOVEQ R1. #50

: amt = 50 if button is 2

BEO DONE

: break

CMP

RO. #3

: is button 3?

MOVEO R1. #100

: amt = 100 if button is 3

BEO

DONE

: break

R1. #0

default amt = 0

MOV

DONE

```

# Estrutura While [Harris and Harris(2016)]

#### **Code Example 6.16 WHILE LOOP**

#### **High-Level Code**

```

int pow = 1;

int x = 0;

while (pow != 128) {

pow = pow * 2;

x = x + 1;

}

```

# Estrutura For [Harris and Harris(2016)]

#### **Code Example 6.17 FOR LOOP**

#### **High-Level Code**

```

int i;

int sum = 0;

for (i = 0; i < 10; i = i + 1) {

sum = sum + i;

}</pre>

```

## Acesso a arranjos [Harris and Harris(2016)]

#### **Code Example 6.18** ACCESSING ARRAYS USING A FOR LOOP

#### **High-Level Code ARM Assembly Code** int i: : R0 = array base address. R1 = iint scores[200]: : initialization code MOV RO. #0x14000000 : RO = base address MOV R1. #0 : i = 0100P CMP R1. #200 · i < 200? for (i = 0: i < 200: i = i + 1)RGF L3 : if i ≥ 200. exit loop LSL R2. R1. #2 : R2 = i \* 4 scores[i] = scores[i] + 10:LDR R3. [R0, R2] ; R3 = scores[i] ADD R3. R3. #10 : R3 = scores[i] + 10 STR R3. FR0. R21 : scores[i] = scores[i] + 10 ADD R1. R1. #1 : i = i + 1100P : repeat loop

# Modos de indexação [Harris and Harris(2016)]

Table 6.4 ARM indexing modes

| Mode       | ARM Assembly      | Address | Base Register |

|------------|-------------------|---------|---------------|

| Offset     | LDR RO, [R1, R2]  | R1 + R2 | Unchanged     |

| Pre-index  | LDR RO, [R1, R2]! | R1 + R2 | R1 = R1 + R2  |

| Post-index | LDR RO, [R1], R2  | R1      | R1 = R1 + R2  |

## Acesso a arranjos com pós-incremento [Harris and Harris(2016)]

#### **Code Example 6.19** FOR LOOP USING POST-INDEXING

## **High-Level Code**

```

; R0 = array base address

; initialization code

MOV R0, #0x14000000 ; R0 = base address

ADD R1, R0, #800 ; R1 = base address + (200*4)

LOOP

CMP R0, R1 ; reached end of array?

BGE L3 ; if yes, exit loop

LDR R2, [R0] ; R2 = scores[i]

ADD R2, R2, #10 ; R2 = scores[i] + 10

STR R2, [R0], #4 ; scores[i] = scores[i] + 10

; then R0 = R0 + 4

B LOOP ; repeat loop

L3

```

## Para saber mais e praticar...

- https://www.arm.com/resources

- https://salmanarif.bitbucket.io/visual/

- https://cpulator.01xz.net/?sys=arm

- https://azm.azerialabs.com/

- https://www.edaplayground.com/x/vcGc

## **Bibliografia**

David Harris and Sarah Harris.

Digital Design and Computer Architecture: ARM  ${\rlap/\!\!R}$  Edition.

Morgan Kaufmann, 2016.